# Innovative packaging by AME technology

DR. RAFAEL DEL REY

August 2023

NASDAQ: NNDM I www.nano-di.com | © 2022 Nano Dimension. All rights reserved.

## Agenda

- Introduction

- Motivation

- AME Packaging History & Process Evolution

- AME Description

- System in Package (SiP) Development Flow

- RF SiP

- Power Transistor AME Packaging

- Summary

## AME Packaging

## Motivation

**CURRENT WORLD OF ELECTRONICS**

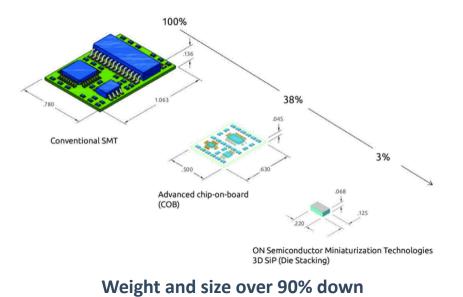

### 1. Limits:

preventing improvement of performance and reduction other factors such as weight and size

NANODIMENSION Electrifying Additive Manufacturing\*

### 2. Supply chains:

hurting most in the high variety small mix and when prototyping (long R&D cycles)

## **Motivation (cont.)**

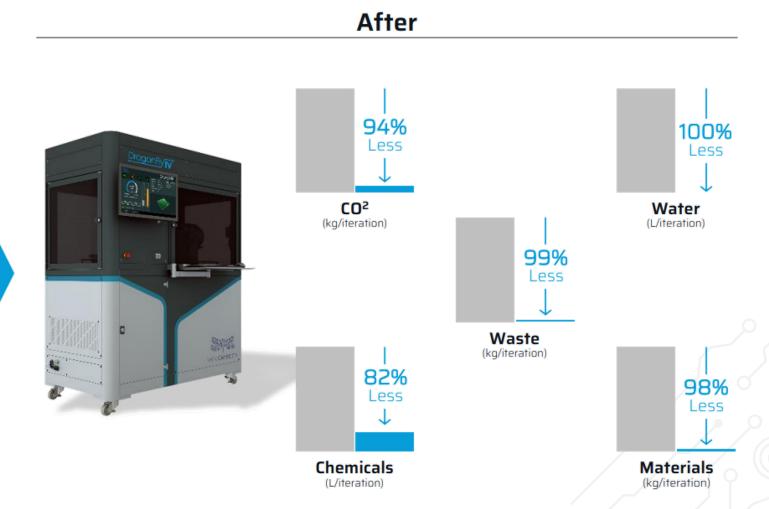

TRADITIONAL MANUFACTURING VS. SUSTAINABLE AM SOLUTIONS

#### 3. Sustainability

A holistic approach towards functional electronics with net zero carbon emissions

## **Motivation (cont.)**

#### TRADITIONAL MANUFACTURING VS. SUSTAINABLE AM SOLUTIONS

Before

1 Based on a 2021 study by HSSMI, a UK based sustainability consultant

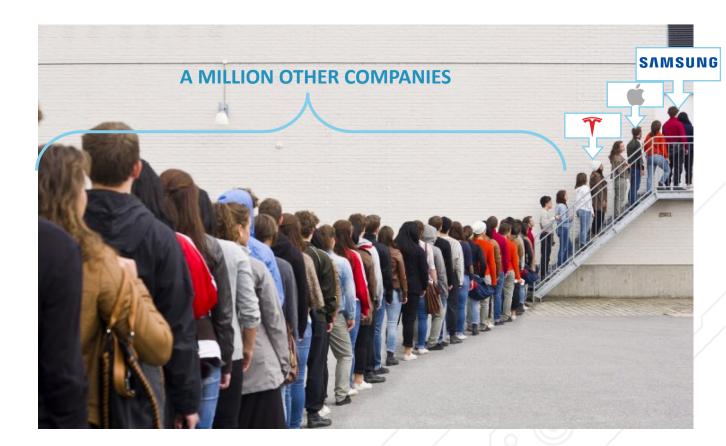

## Motivation (cont.)

LONG LINES FOR PACKAGING AND PROTOTYPING

Very long lead time for small & medium-sized enterprises and very long R&D-cycles

- To produce a prototype, 4 R&D cycles are required

- each cycle has a 3-4 months lead time until supplied from the global packages & electronics manufacturer

# History

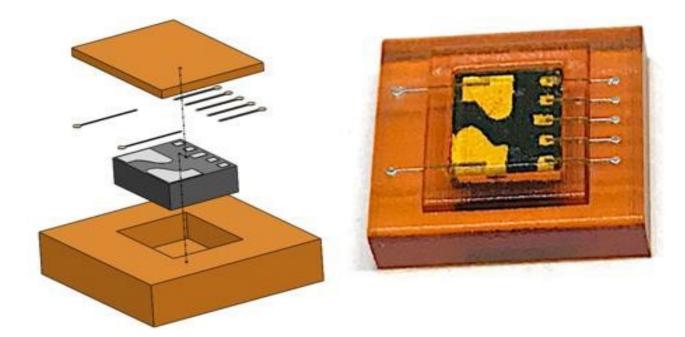

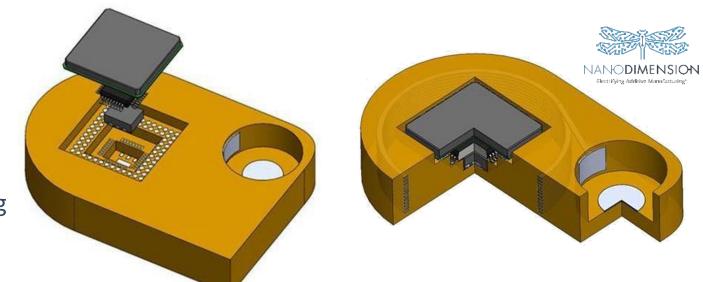

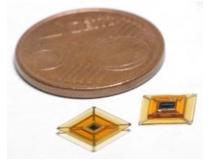

### AME SOCKETS & INTERPOSERS

• Very first encapsulation concept: Stacking of packaged ICs and interposers

Source: J.A.M.E.S NASDAQ: NNDM I www.nano-di.com ¦ © 2022 Nano Dimension. All rights reserved.

# History (cont.)

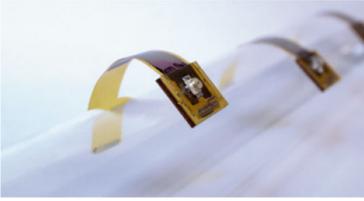

### AME SENSOR APPLICATIONS

9

Artificial Hair Cells for Flow Sensing

EMBEDDING FLOW SENSORS IN SEALED PACKAGE

Sensor direct print packaging (3D printed wirebonding)

Compact and flexible meander antenna for Surface Acoustic Wave sensors

3D embedded sensor in electrical packaging

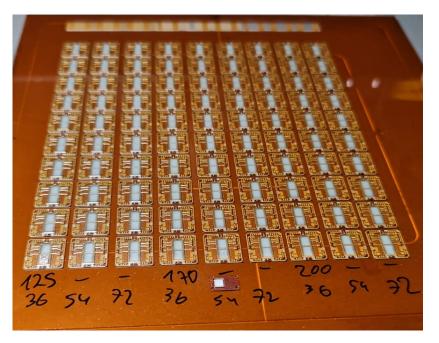

# History (cont.)

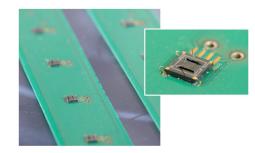

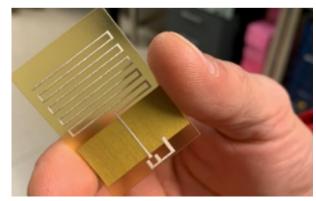

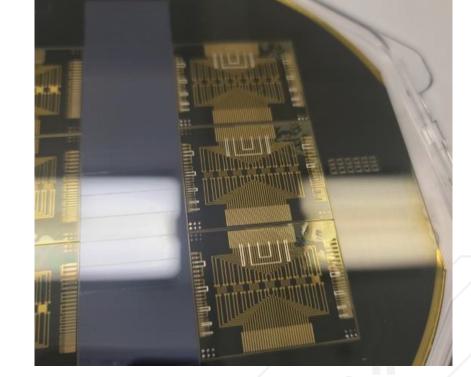

**TESTPATCH AGCITE® BONDING**

Print on foil

Print on wafer

## **Process Evolution**

Face up vs Face (3.5W) down Passive **SiP electrical** Wire bonding less measurement Repeatability Wire bonding less **IC Substrate** Alignment **Die embedded** PoC Desing optimization

#### PROCESS PLANNING, SYSTEM DESIGN AND DIE IMPLEMENTATION

NASDAQ: NNDM I www.nano-di.com | © 2022 Nano Dimension. All rights reserved.

NANODIMENSION

**Functional SiP**

## But how it works?

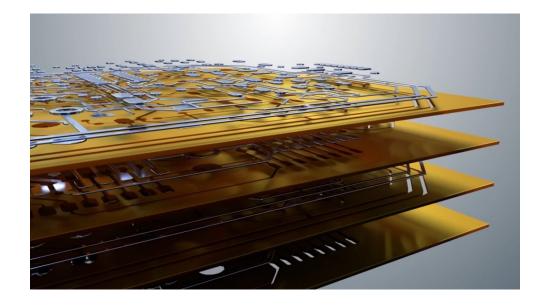

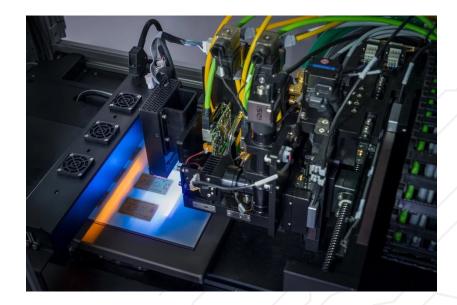

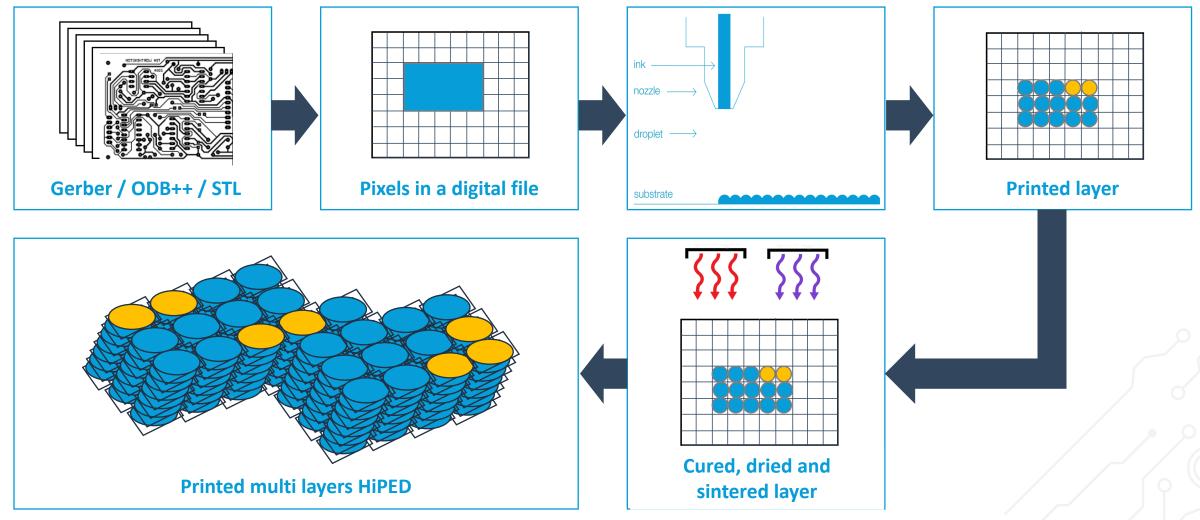

#### ADDITIVE MANUFACTURING ELECTRONICS (AME) - PROCESS DESCRIPTION

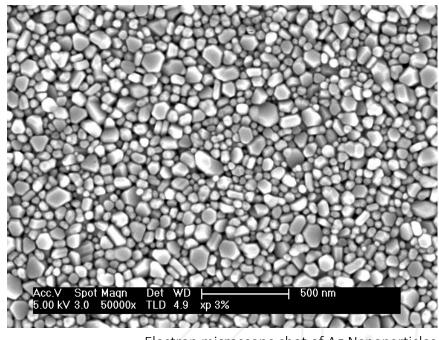

- Inkjet technology that combines UV-cured dielectric material (acrylic monomers) with silver nanoparticles (Ag NP) that undergo sintering upon IR radiation.

- Result in solid objects with highly conductive patterns in shapes unachievable through traditional processes

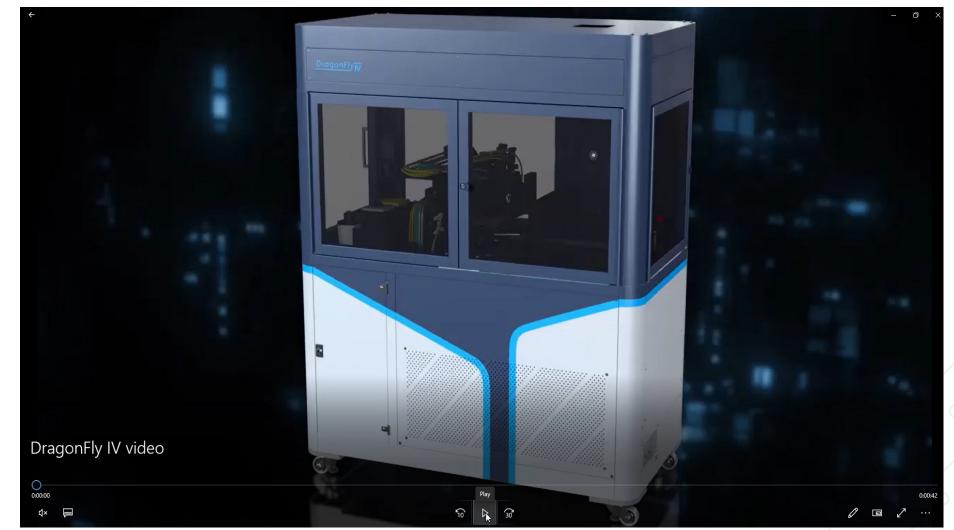

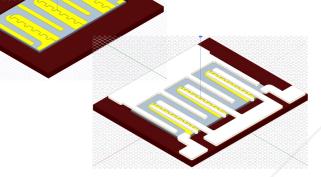

## **Additive Manufacturing Electronics (AME) - DragonFly**

>

14

## From a Digital design file to a Printed Hi-PED

15

## **AME Build**

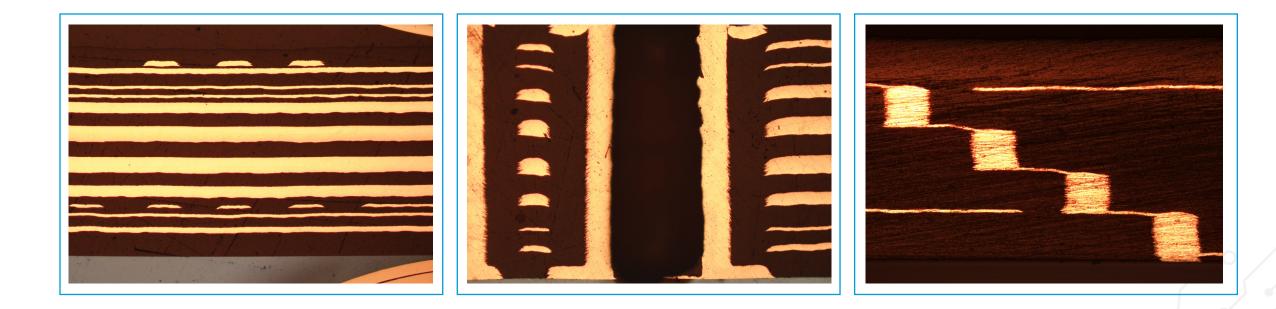

#### **CROSS-SECTIONAL VIEW**

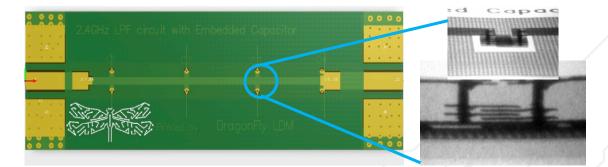

## **RF Examples**

HIGH FREQUENCY FILTERS

• Complex tuning iterations and extra laser trimming process is replaced by an overnight print

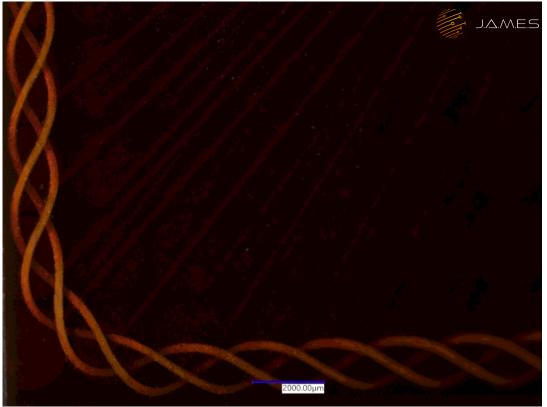

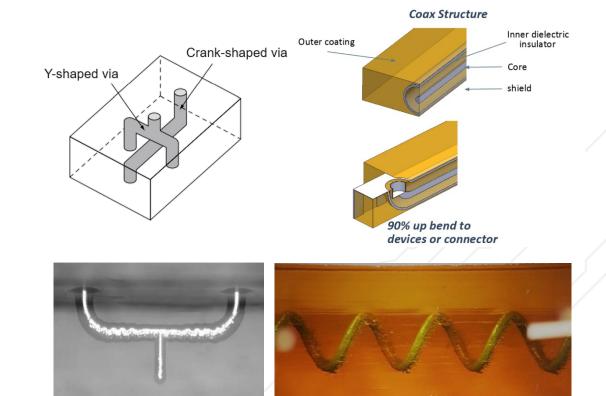

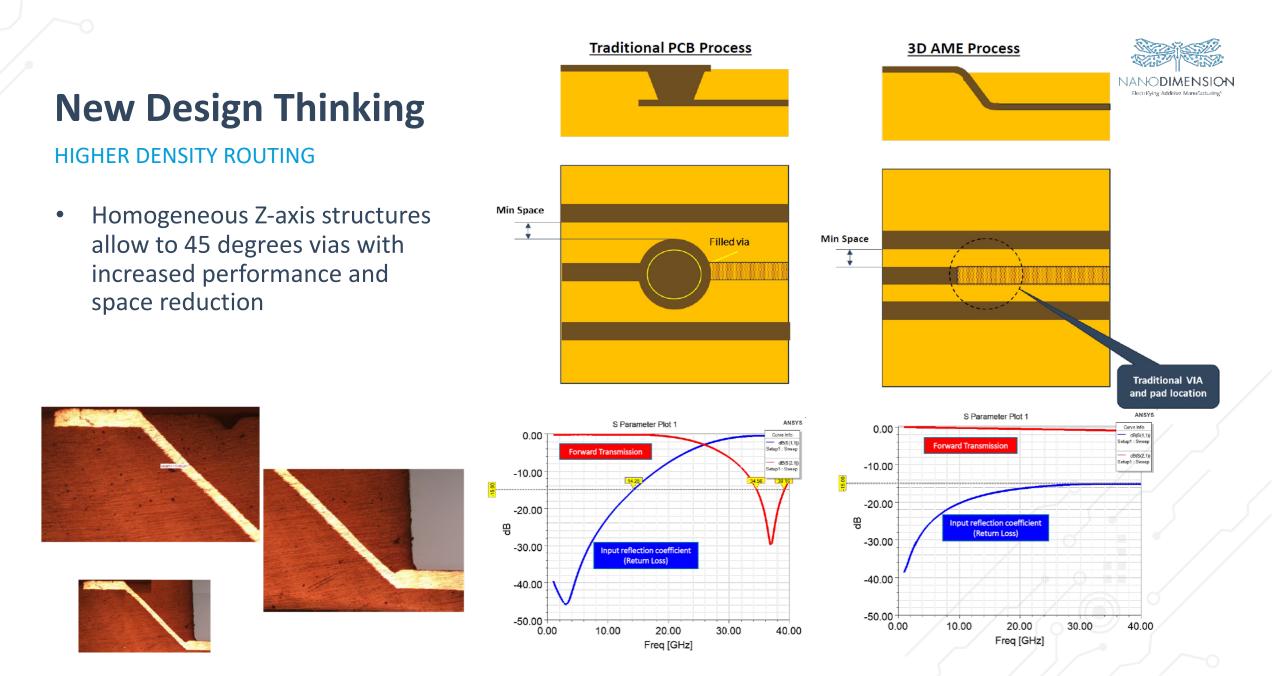

## **New Design Thinking**

NON PLANAR TRANSMISSION LINES

• Coaxials, twisted pairs, waveguides. Freedom of via interconnects

Source: J.A.M.E.S

## **New Design Thinking**

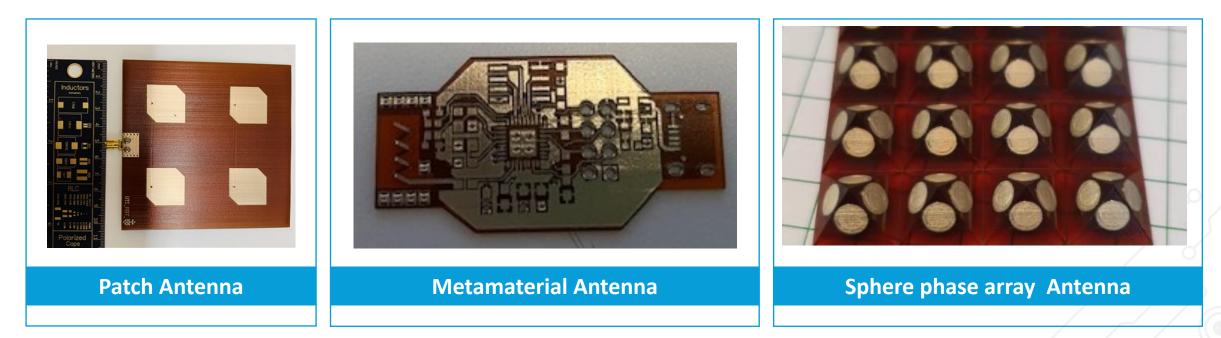

#### **3D-PRINTED ANTENNAS AND RESONATORS**

- AME technology is an enabler for new designs of antennas

- Design freedom in the 3D space enables unique antennas such as: Omni directional antennas, coils antennas, special shaped phased-array antennas, etc.

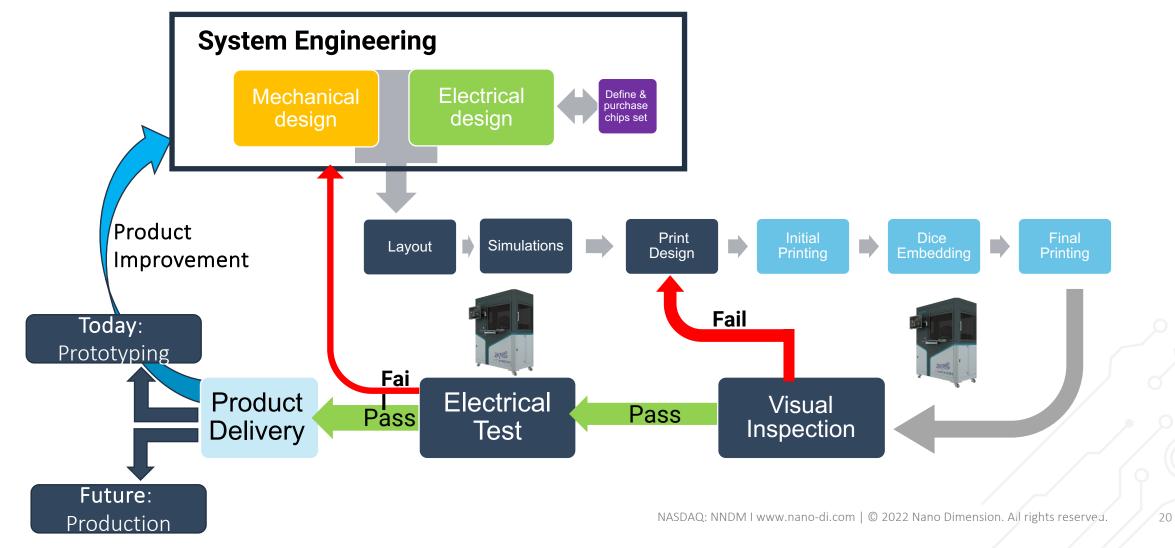

## System in Package (SiP) development flow

PROCESS PLANNING, SYSTEM DESIGN AND DIE IMPLEMENTATION

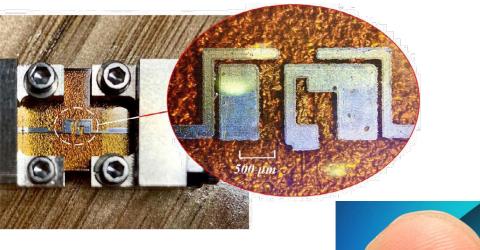

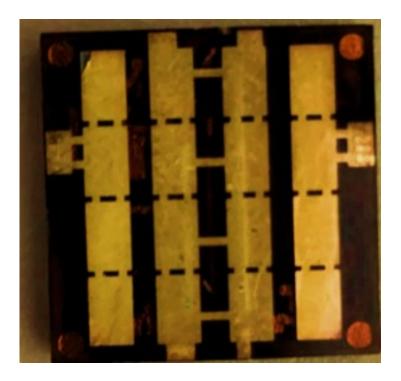

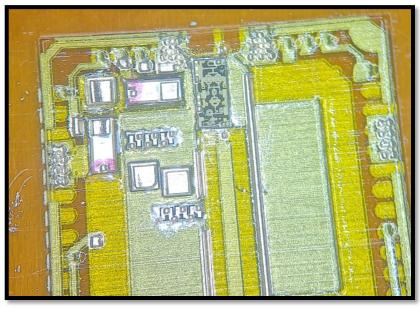

### **RF SiP**

## Schematic

- Main component:

- MMIC 4W X-band die(QPA1022D)

- Other: Resistors (6),

capacitors (3) and MOSFET

dies.

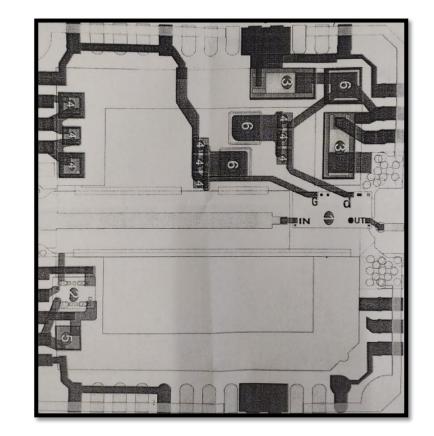

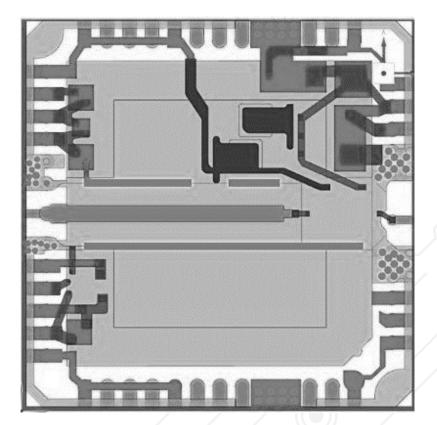

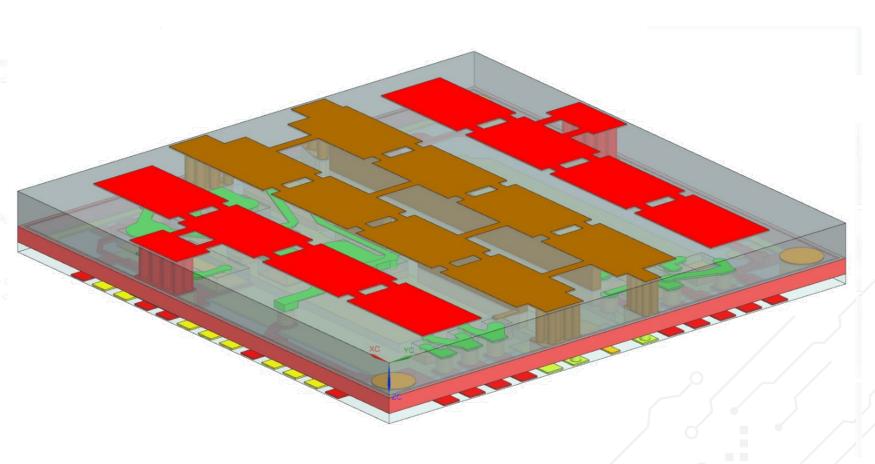

## Layout and BOM

- Main component:

- MMIC 4W X-band die(QPA1022D)

- Other: Resistors (6),

capacitors (3) and MOSFET

dies.

- Overall physical dimensions:

- o 13.2x13.2x1.5mm

- Minimum pad size on die

80um.

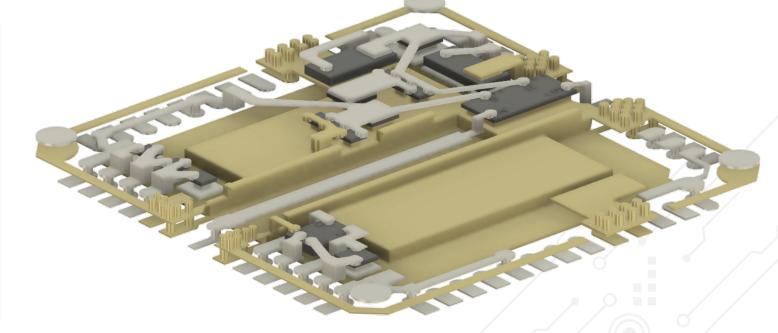

### Layout and BOM –cont'

- - Main 50-Ohm line

• QFN on bottom side.

• Shielding for the RF line (walls)

### Layout and BOM -cont'

• Before components placement

### Layout and BOM –cont'

• Before components placement

## Layout and BOM -cont'

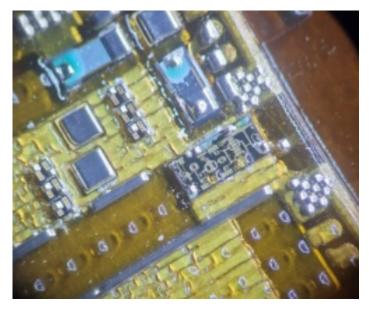

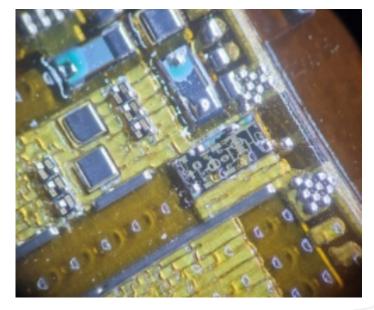

• After components placement

## Layout and BOM –cont'

• Before components placement

• After components placement.

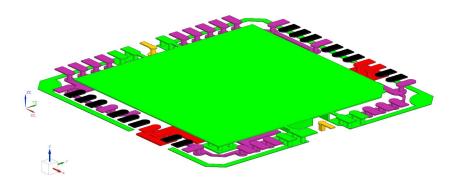

## Layout and BOM –cont'

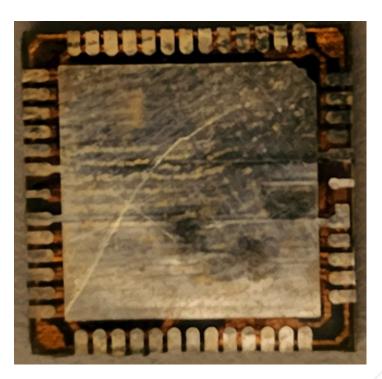

• FINAL TOP & BOTTOM VIEW

### **AME Packaging Processes**

## **Top level processes available**

Split Assembly

Manual placement of Die is possible

### Flip Chip

### High Accuracy Automatic placement is required

NASDAQ: NNDM I www.nano-di.com | © 2022 Nano Dimension. All rights reserved.

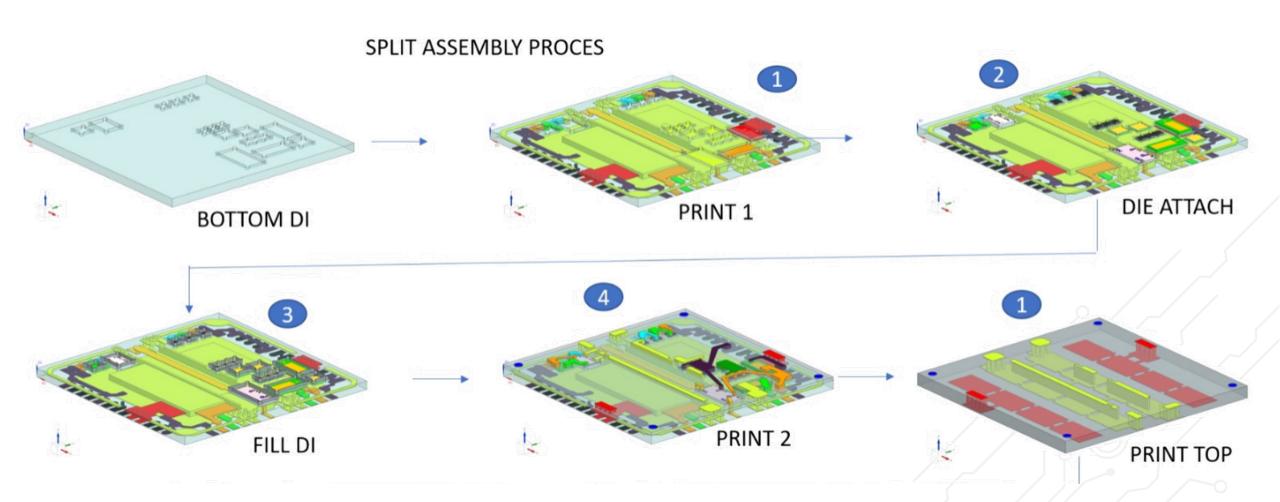

## **Split Assembly**

## **Split assembly process**

34

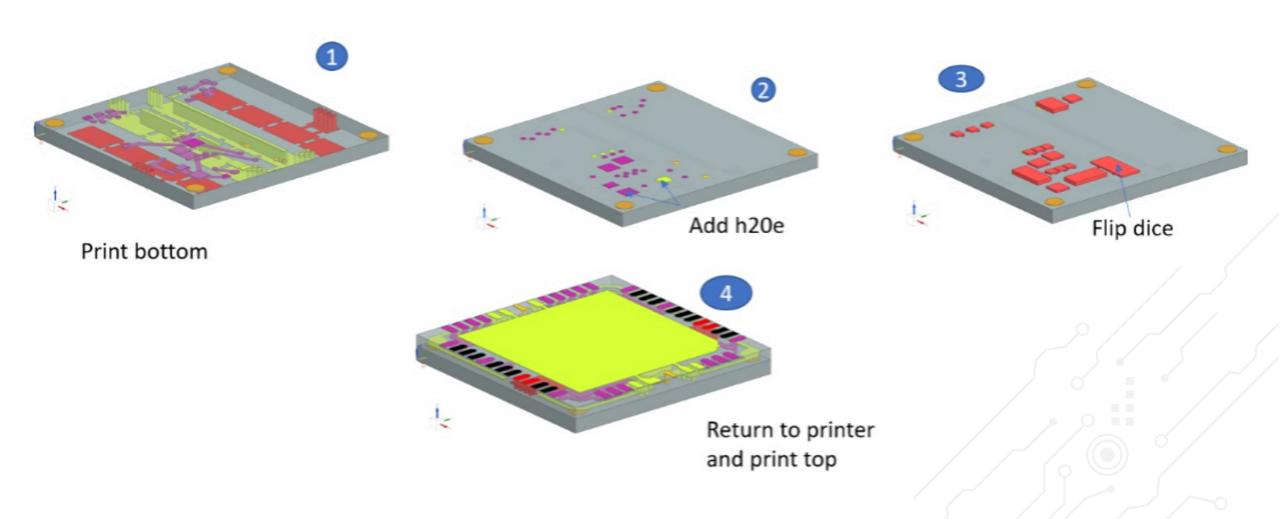

## Flip-Chip

## Flip chip assembly process

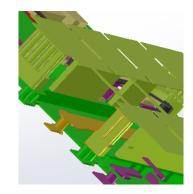

### **Main Process Challenges**

#### • Registration:

- Dies placement.

- Building up the VIAS on top of the dies

- Removing print for P&P.

- Pushing the current boundaries of design rules and process.

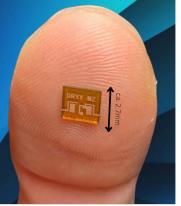

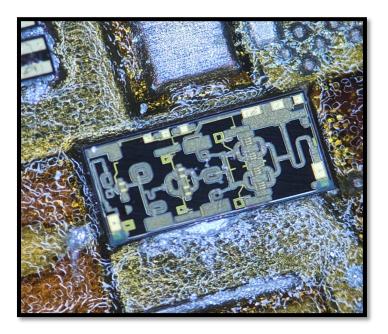

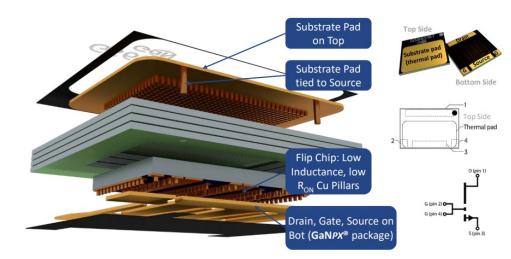

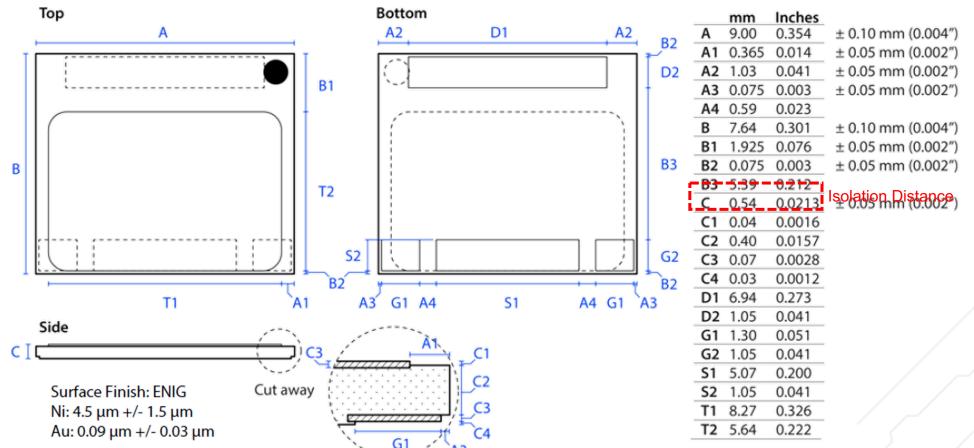

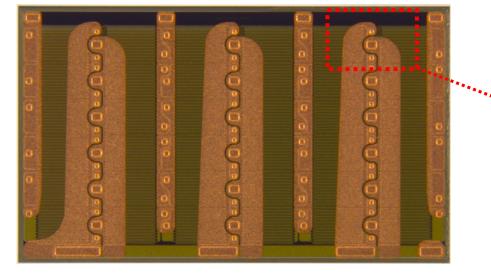

### **GAN-ON-SILICON**

- Enhancement mode GaN-on-silicon power transistor (650V)

- Top-side cooled configuration

- High current Ids(max) = 60A

- $\operatorname{Rds}(on) = 25m\Omega$

- Very high switching frequency (> 100MHz)

- Small 9 X 7.6 mm PCB footprint

|                                       |   | -    |   | -   | C. |

|---------------------------------------|---|------|---|-----|----|

| 1 100                                 |   | 6    | 0 | 66  |    |

|                                       | 9 |      |   | 5   |    |

|                                       | 2 | č    | 2 | 6   |    |

|                                       |   | 8    |   | S   |    |

| 0                                     |   | 2    |   | 2   |    |

|                                       |   | S    |   | No. |    |

|                                       | 0 | 0 55 | 0 | 0   |    |

| • <u> </u>                            | 0 | Q    | 0 | Q   |    |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0 |      | 0 | ŭ   |    |

| 0                                     |   | 0    | 8 | 0   |    |

|                                       |   |      |   |     |    |

| 6                                     | a | 6    | 0 | 6   |    |

GAN SYSTEMS (GS66516T)

### **Package Dimensions**

40

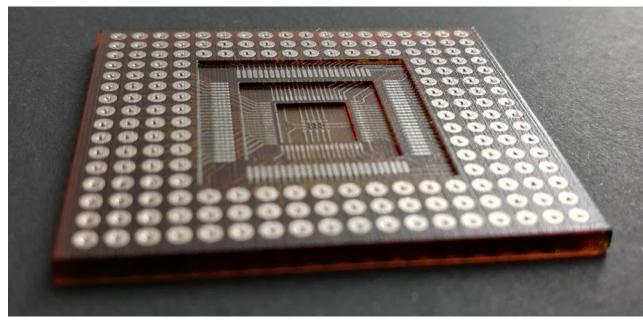

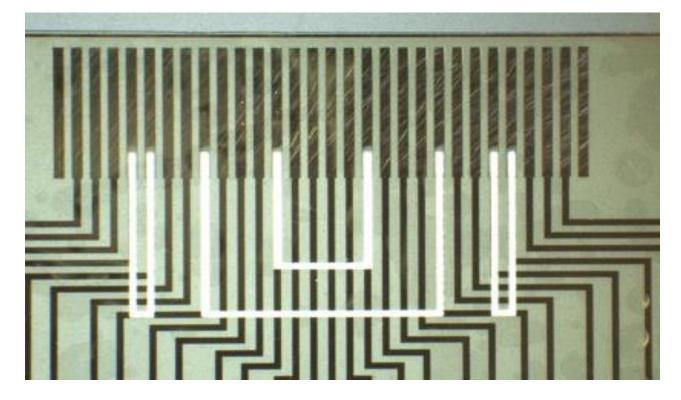

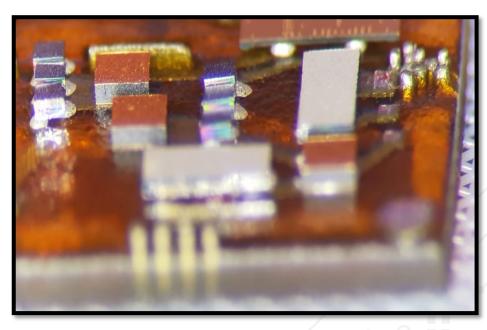

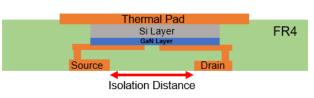

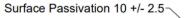

### GAN SYSTEMS (GS66516T) PAD GEOMETRY

- Metallization: Cu (thickness= 8um +/- 2um)

Passivation (total thickness= 10um +/- 2.5um):

Very top passivation: polyimide (thickness= 5um +/-1.5um)

Below Polyimide: SiO2 and SiN passivation.

- Die total thickness: 8 (Cu)+10 (Passivation)+240 (Si/GaN/AI)+4(Cu)=262 um

#### X-X Cross section

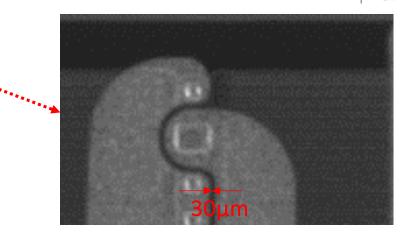

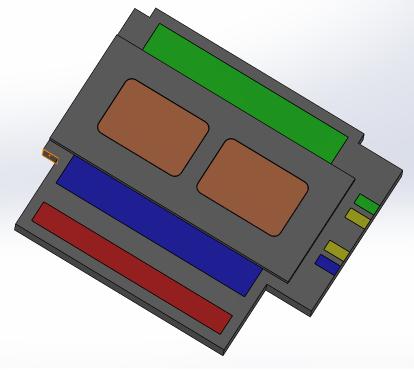

**RI.SE DESIGN FOR AME**

Challenges:

- Meeting the application targets High voltage, high current

- Effective heat dissipation High current

43

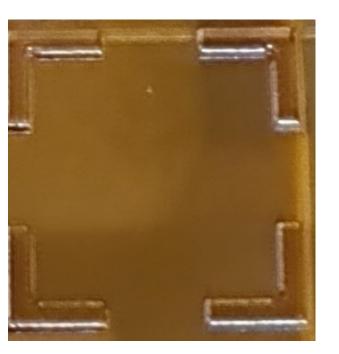

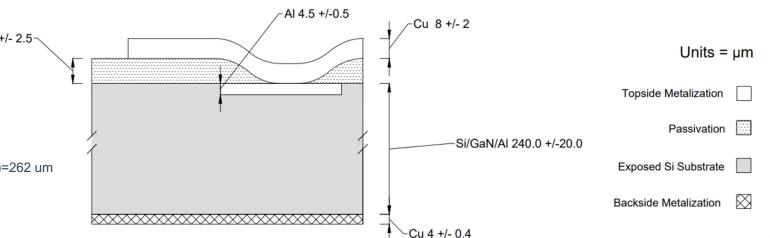

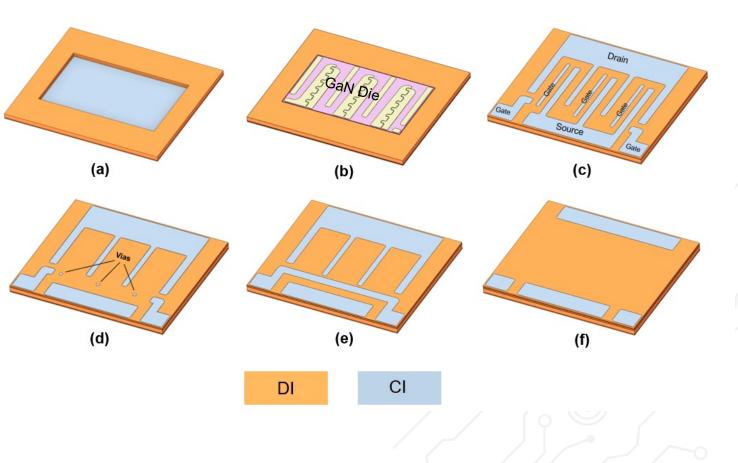

### **Power Transistor SiP**

#### **GAN-ON-SILICON**

### Process:

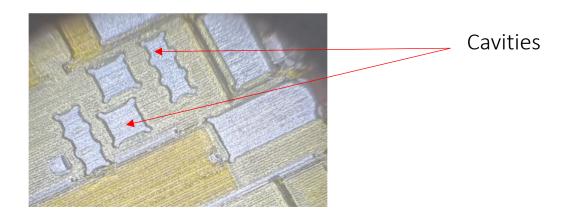

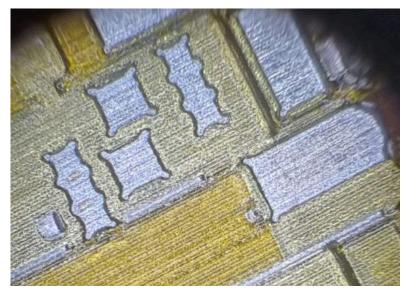

- a) Printing dielectric cavities & pause the print (keeping chuck at 100°C)

- b) Placing the silicon dies and adding Epotek conductive glue on the bare pads

- c) Print DI "soldermask alike" and fill gaps

- d) Print CI pads connection

- e) Print interconnecting tracks

- f) Print cover layer

#### **GAN-ON-SILICON**

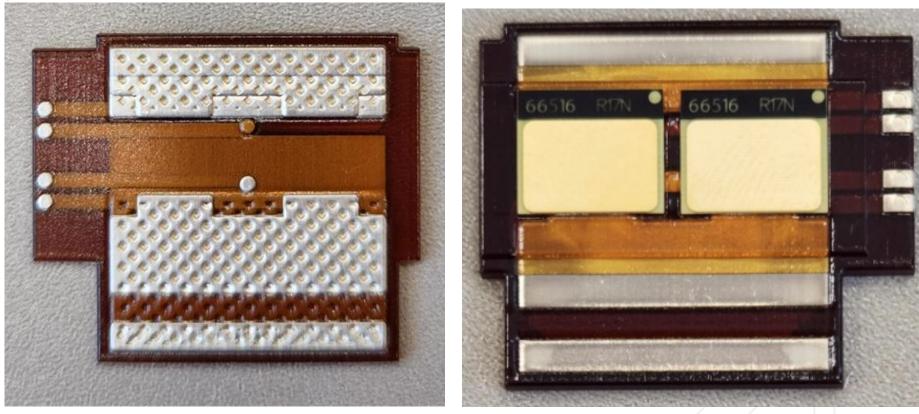

**GAN-ON-SILICON**

### Resulting package

46

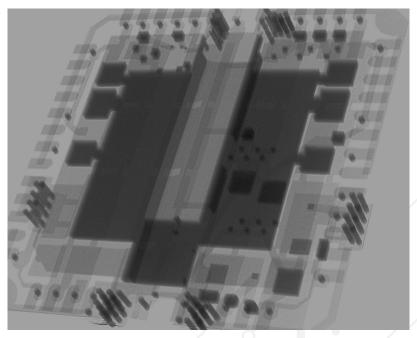

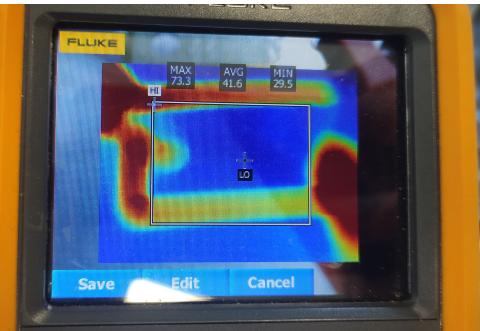

### **Power Transistor SiP**

**GAN-ON-SILICON**

Tests:

• 38Amp @ room temp (25°C)

47

### Summary

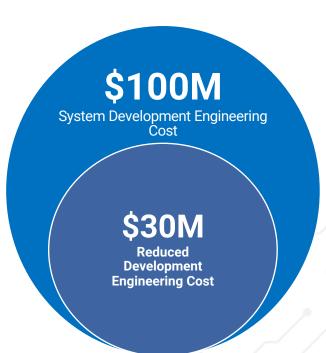

# Nano's Fooprint in Silicon Packaging

SIGNIFICANT IMPROVEMENT IN GTM TIME + SPEC

R&D cycle – 90% down

Taking down rapid prototyping from **12 month to 2 month**  Testing cycle optimization – Test silicon device during development stage

#### Estimated prototyping market size

# Nano's Fooprint in Silicon Packaging (cont.)

#### PERFORMANCE IMPROVEMENT

• Wirebondingless connections: Transmission lines' interconnects can be controlled by design

# SiP & Packaging Market Share

FUTURE - PROCESS PLANNING, SYSTEM DESIGN AND DIE IMPLEMENTATION

**Further improvements towards production** With improvement of our materials, We can produce immediate high mix low volume RF SIPs

SiP production market size Growing market – 8% CAGR till 2030

\*With few big legacy players, it's a highly concentrated market, ready to be disturbed

# Thank you!

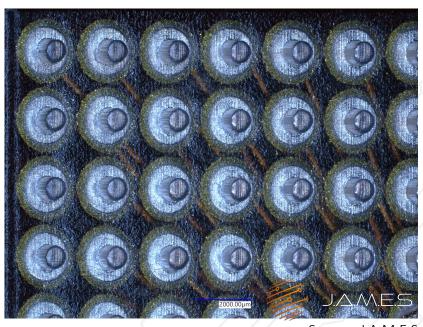

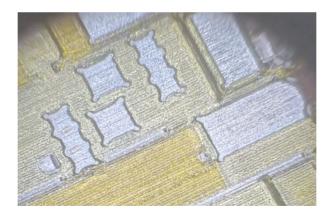

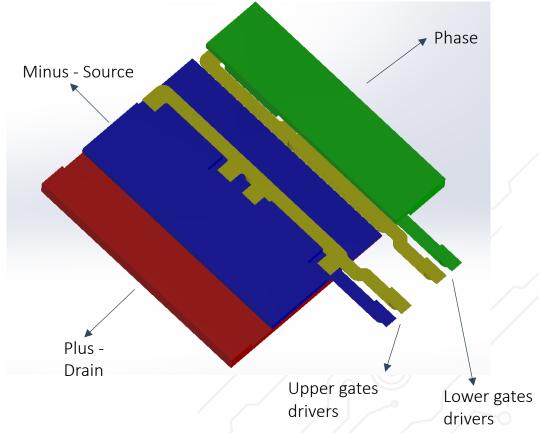

#### **UNLEASH AME POTENTIAL – APPLIED PHYSICS**

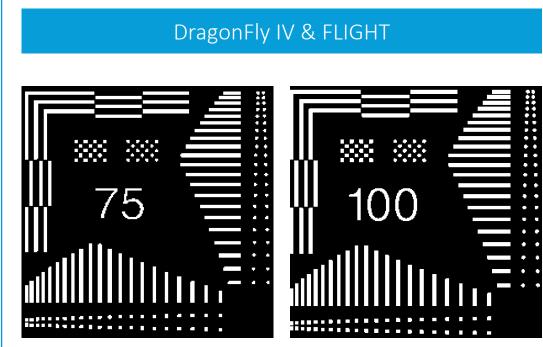

- Dimensional accuracy, slice over slice.

- AgCite<sup>™</sup> Nanoparticle Silver Ink

Resolution Accuracy coupons

51

Electron microscope shot of Ag Nanoparticles